Greg Papadopoulos EVP and CTO Sun Microsystems, Inc.

# **Takeaways**

- Business demands fuel IT demand

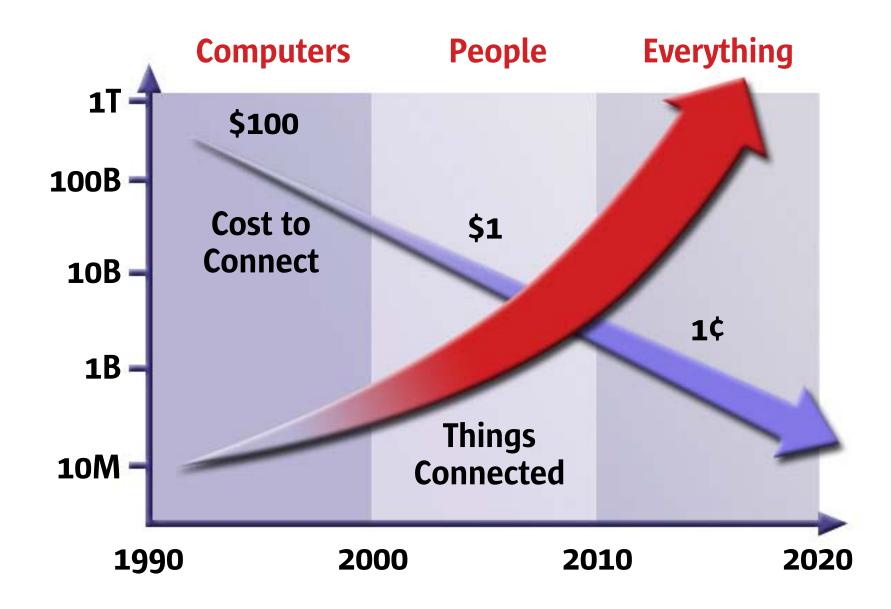

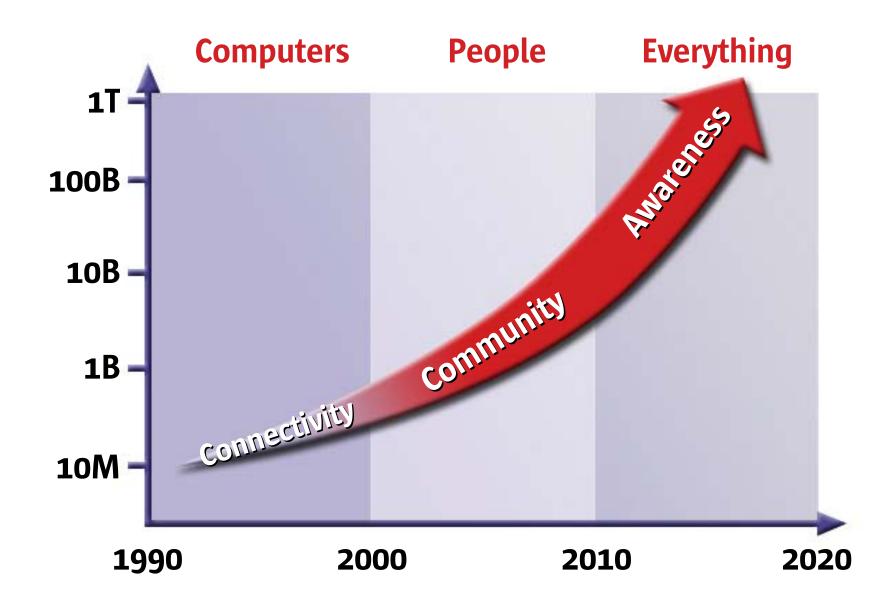

- Still in the first phases of network computing

- Decision point

- Mask complexity through people or eliminate through engineering

- Innovation matters

## The Revolution

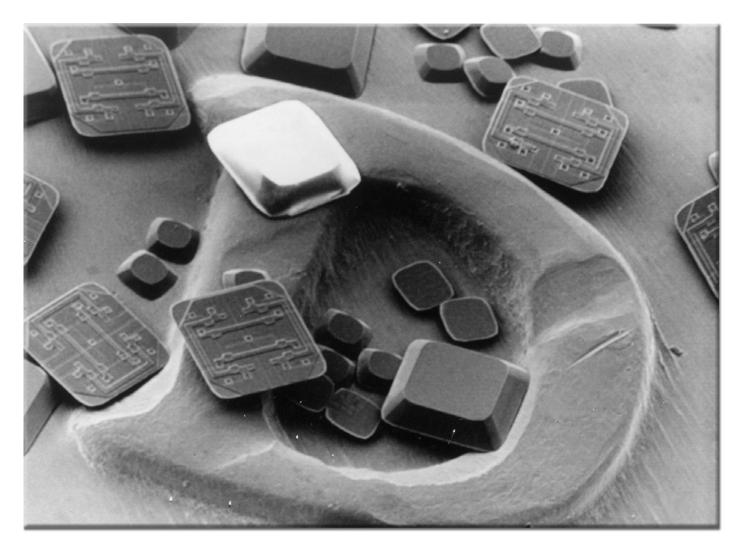

# **RFID**

# The Revolution

### **Bottom Line**

- Still in the first phases of networking

- Expect the number of networked things to grow by another factor of 1M

- New value from automating still-manual processes

- Expect radical transformation of SW and systems

- Systems, in particular, are at a watershed

- Mask complexity through people or eliminate through engineering

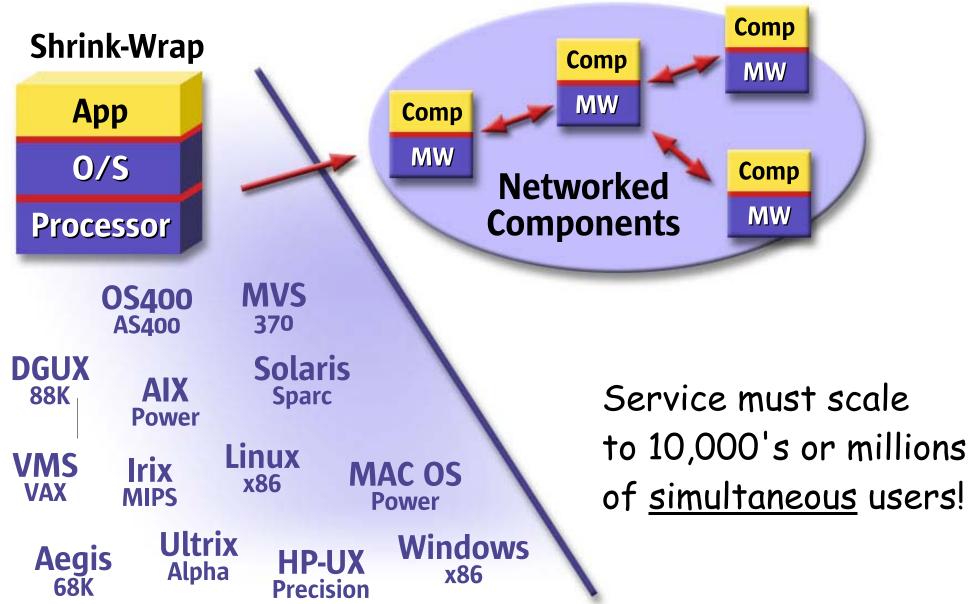

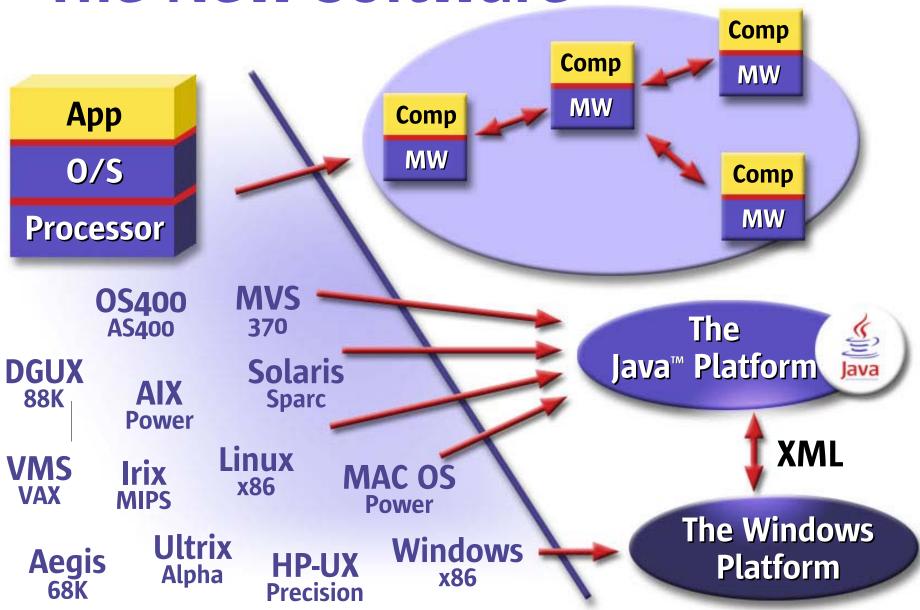

### The New Software

#### **Shrink-Wrap**

OS400 AS400

BSK AIX Power

VMS VAX

Irix MIPS

IPS

Aegis Ultrix

Alpha

MVS 370

> Solaris Sparc

> > **HP-UX**

**Precision**

Linux x86

MAC OS Power

> Windows x86

Application scales from 1 to perhaps 100's of users

For Desktop:

1 copy SW = 1 copy HW

### **The New Software**

### The New Software

# The Operations Challenge

#### Was...

- Availability

- Performance

- Scale

Price/ Performance

# The Operations Challenge

#### Was...

- Availability

- Performance

- Scale

Price/

Performance

### Becoming...

- Service Level

- Efficiency

- Security

**Total Cost of Service Level**

# The Emperor Has No Clothes

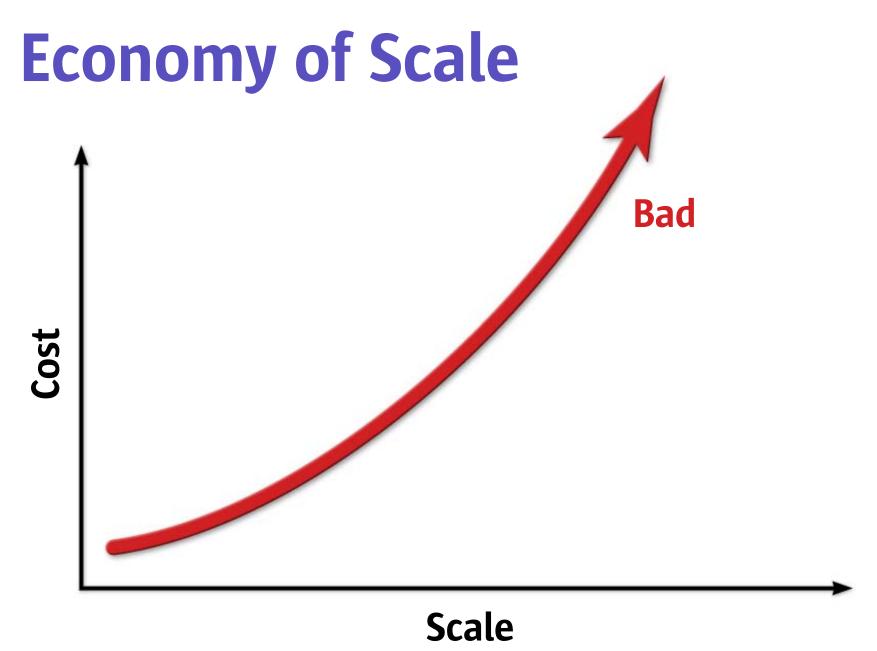

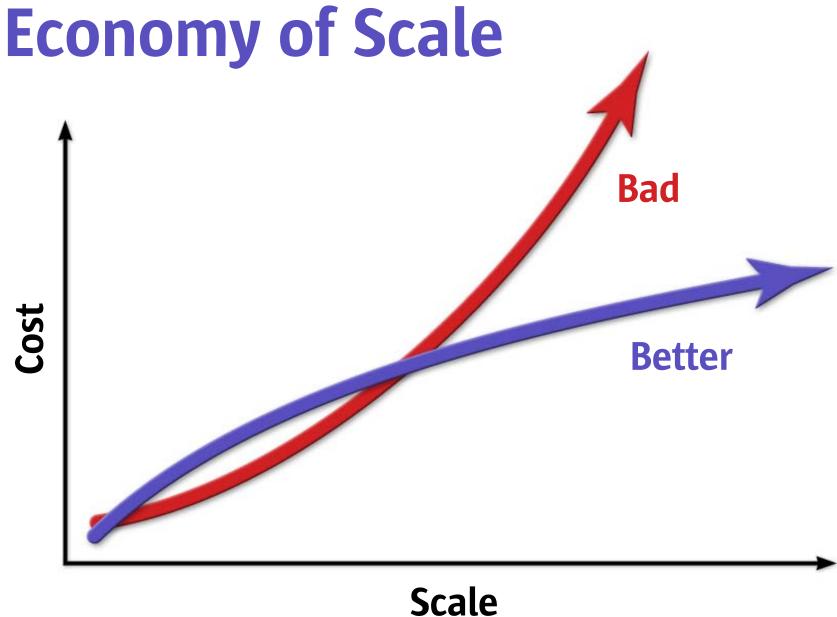

- Network computing is wildly complex: no discernible economy of scale

- 75+% of IT budgets going to people + operations

- 15–20% typical utilization

- Out of the \$2.4T WW ICT spending only a tiny fraction goes to HW/SW systems

### **Decision Point**

# Mask Complexity or Engineer It Away

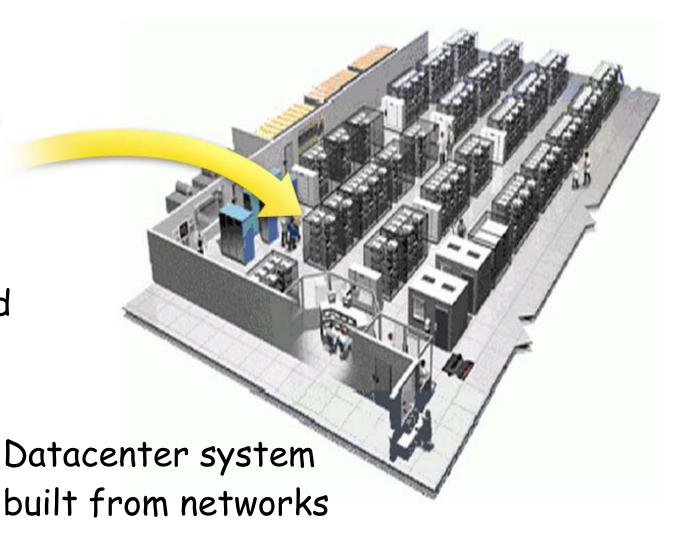

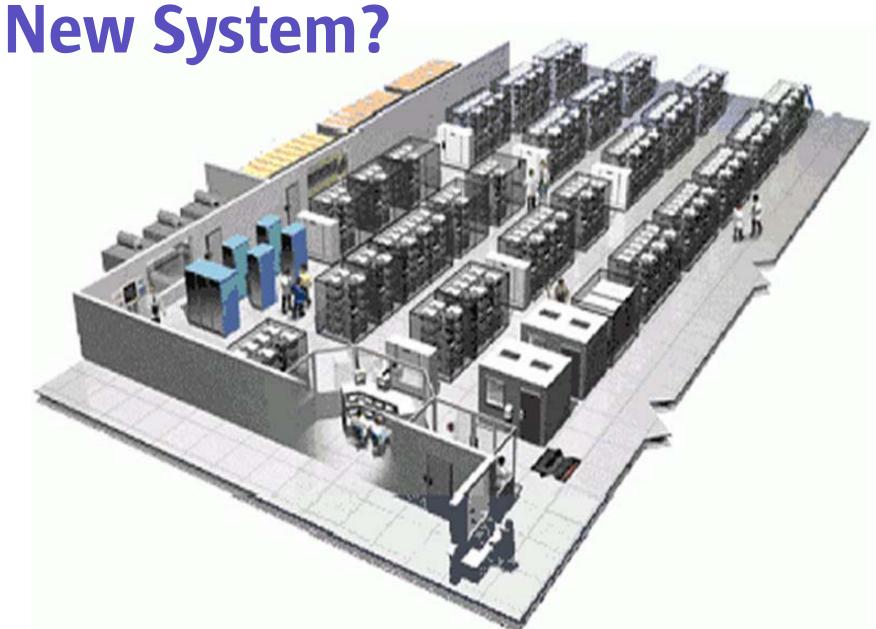

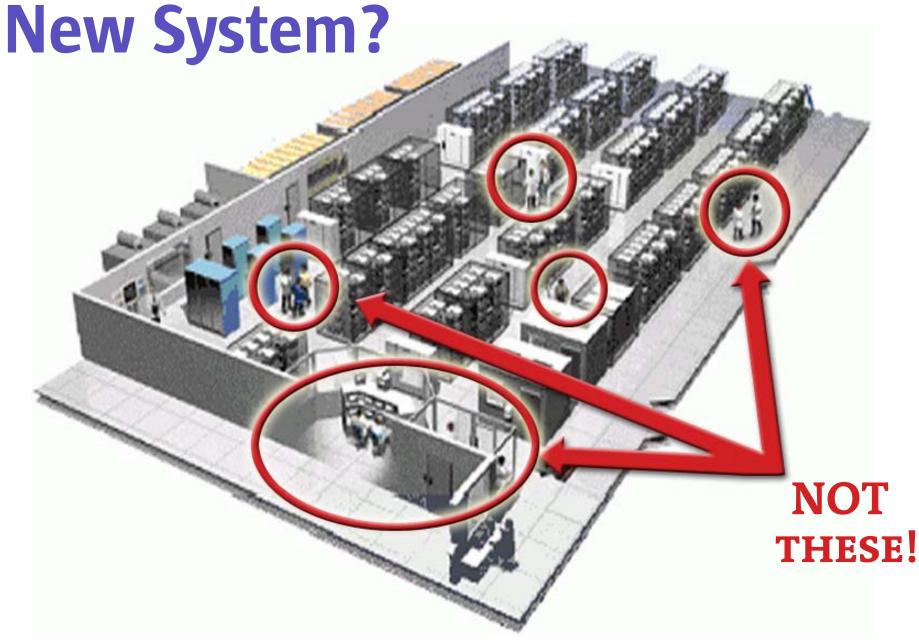

# Old Systems Are Components in the New One

Server connected to networks

# Old Systems Are Components in the New One

Server connected to networks

What Is O/S for This

What Is O/S for This

Now System?

# **Grid Computing Today at Sun**

# 13,500 CPUs in 3 cities for processor design

- SPARC microprocessor design facilities in Sunnyvale, Austin, Burlington

- Sites use a departmental Cluster Grid approach normally

- Workload is distributed across all sites in an Enterprise Grid approach to meet peak load requirements

22 years compute time/day 98% average CPU usage 24/7/365

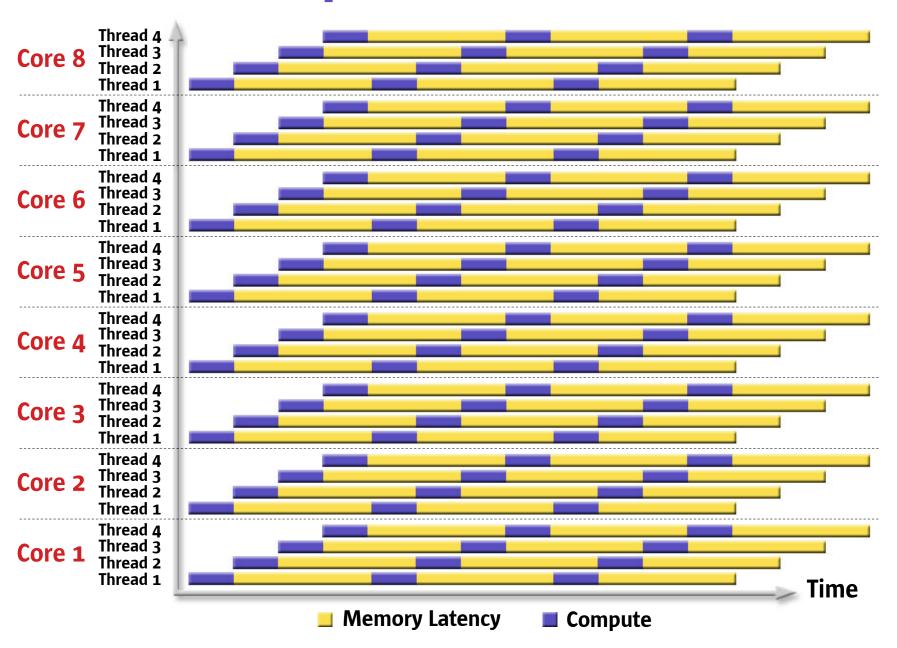

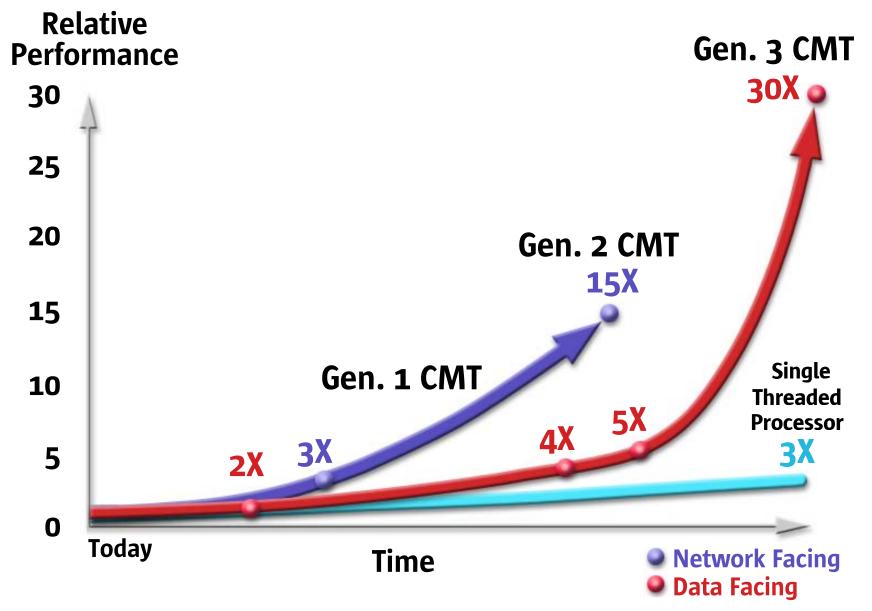

# THROUGHPUT COMPUTING

- New design approach for the UltraSPARC® processor family

- Eclipses throughput of today's processors by a magnitude of up to 15-30x

- Quantum reduction in the cost of network computing — without software disruption

# The Big Bang Is Happening — Four Converging Trends

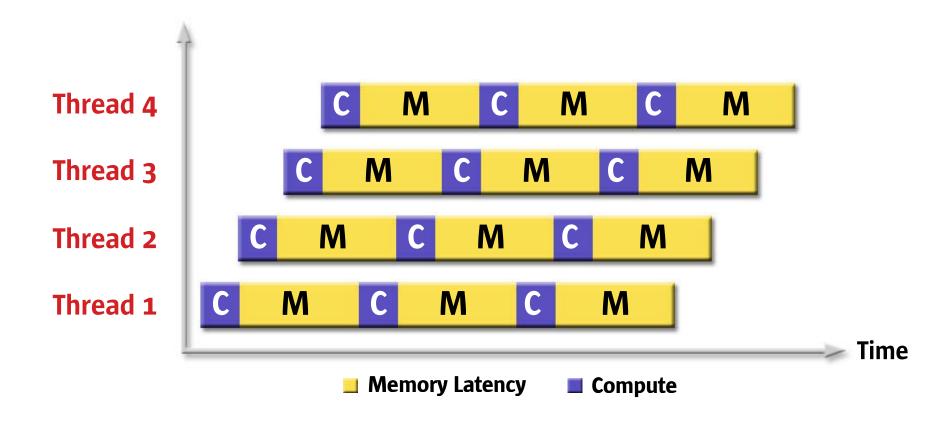

# Network Computing Is Thread Rich

Web services, Java<sup>™</sup> applications, database transactions, ERP...

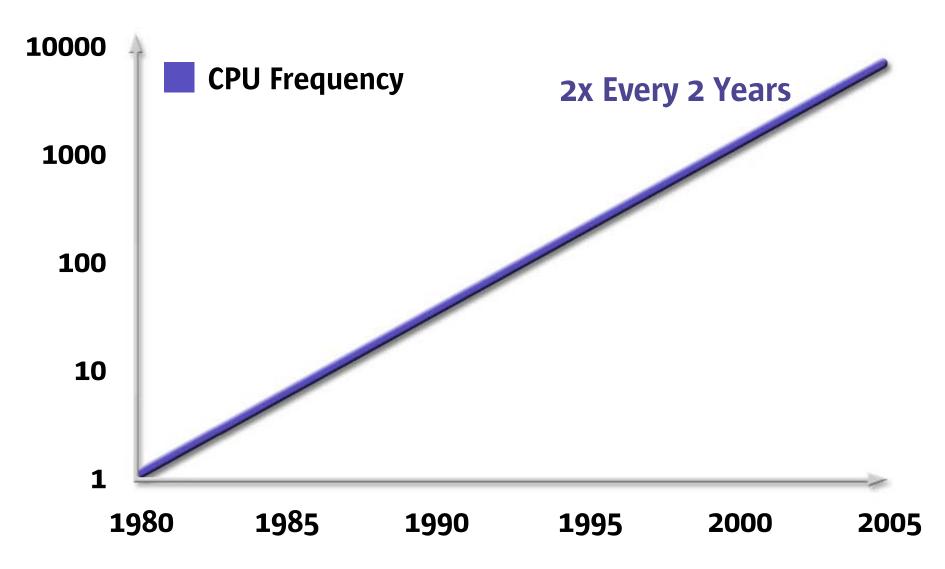

#### Moore's Law

A fraction of the die can already build a good processor core; how am I going to use a billion transistors?

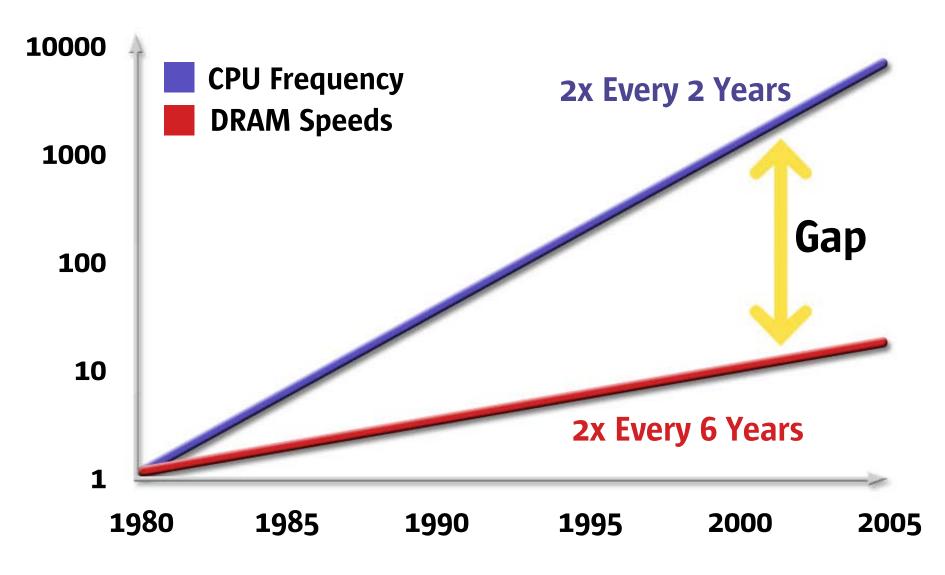

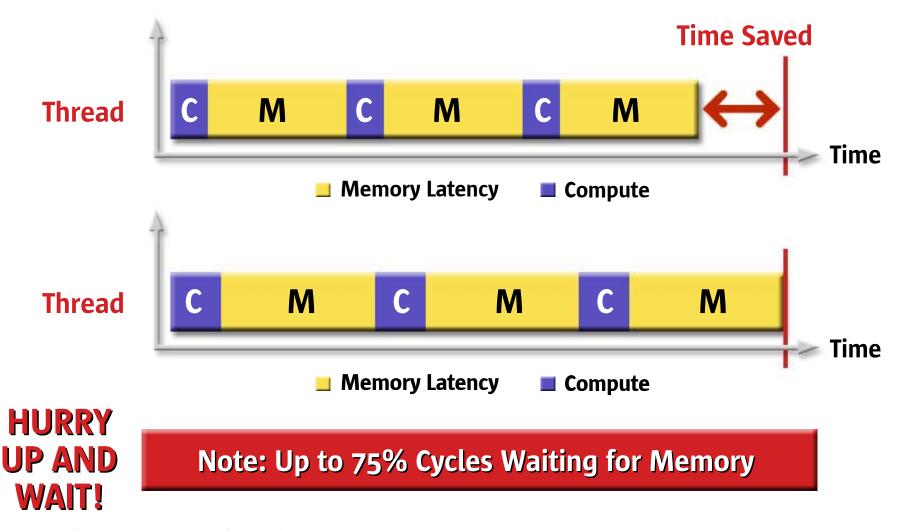

# Worsening Memory Latency

It's approaching 1000s of CPU cycles! Friend or foe?

# **Growing Complexity** of Processor Design

Forcing a rethinking of processor architecture – modularity, less is more, time-to-market

# **Memory Bottleneck**

#### **Relative Performance**

# **Memory Bottleneck**

#### **Relative Performance**

# Typical Complex High Frequency Processor

<sup>\*</sup>Source: Microprocessor Report, Richard Sites, It's the Memory, Stupid!, August 1996

# Chip Multithreading (CMT)

# **CMT**—Multiple Multithreaded Cores

# **Throughput Computing**

# **UltraSPARC® IV**

#### 1st GENERATION CMT PROCESSOR FOR MID/HIGH END SYSTEMS

- First milestone in Sun's Throughput Computing roadmap

- Up to twice the throughput of today's UltraSPARC III processor

- Protects customer investment in hardware, software and staff

- Upgrade path

- Binary compatibility across time and product line

# The Three Waves of SPARC Innovation

**CMT SMP** Price/Performance RISC 1980 2010 1990 2000

# **Takeaways**

- Business demands fuel IT demand

- Exponential demand as everything becomes connected

- Decision point

- Eliminate complexity through engineering

- Innovation from Sun

- In Software

- In Systems

Greg Papadopoulos EVP and CTO Sun Microsystems, Inc.